- Författare Lynn Donovan donovan@answers-technology.com.

- Public 2023-12-15 23:53.

- Senast ändrad 2025-01-22 17:41.

VHDL och Verilog anses vara digitala designspråk för allmänna ändamål, medan SystemVerilog representerar en förbättrad version av Verilog . VHDL har rötter inthe Ada programmeringsspråk i både koncept och syntax, medan Verilogs rötter kan spåras tillbaka till en tidig HDL som heter Hilo och programmeringsspråket C.

Folk frågar också, vilket är bättre VHDL eller Verilog?

VHDL är mer omfattande än Verilog och it har också en icke-C-liknande syntax. Med VHDL , har du större chans att skriva fler rader kod. Verilog har en bättre förstår hårdvarumodellering, men har en lägre nivå av programmeringskonstruktioner. Verilog är inte så omfattande som VHDL så det är därför den är mer kompakt.

Dessutom, vad är användningen av Verilog? Verilog är ett hårdvarubeskrivningsspråk; ett textformat för att beskriva elektroniska kretsar och system. Tillämpas på elektronisk design, Verilog är avsedd att användas för verifiering genom simulering, för timinganalys, för testanalys (testbarhetsanalys och felgradering) och för logiksyntes.

På detta sätt, vad är skillnaden mellan Verilog och SystemVerilog?

Den huvudsakliga skillnaden mellan Verilog och SystemVerilog är det Verilog är ett Hardware DescriptionLanguage, medan SystemVerilog är ett språk för hårdvarubeskrivning och maskinvaruverifiering baserat på Verilog . I korthet, SystemVerilog är en förbättrad version av Verilog med ytterligare funktioner.

Vad är VHDL i VLSI?

VLSI Design - VHDL Inledning. Annonser. VHDL står för mycket höghastighets integrerad krets hårdvarubeskrivningsspråk. Det är ett programmeringsspråk som används för att modellera ett digitalt system genom dataflöde, beteende och strukturell modelleringsstil.

Rekommenderad:

Vad är skillnaden mellan Pebble Tec och Pebble Sheen?

Pebble Tec är gjord av naturliga, polerade småsten som skapar en ojämn textur och en halkfri yta. Pebble Sheen innehåller samma teknik som Pebble Tec, men använder mindre småsten för en snyggare finish

Vad är skillnaden mellan en kognitiv psykolog och en kognitiv neurovetare?

Kognitiv psykologi är mer fokuserad på informationsbehandling och beteende. Kognitiv neurovetenskap studerar den underliggande biologin för informationsbehandling och beteende. kognitiv neurovetenskap i centrum

Vad är skillnaden mellan montering och demontering?

är att assembly är (beräkning) i Microsoft net, en byggsten i en applikation, liknande en dll, men innehåller både körbar kod och information som normalt finns i en dlls typbibliotek. Typbiblioteksinformationen i en assembly, kallad manifest, beskriver offentliga funktioner, data, klasser och version

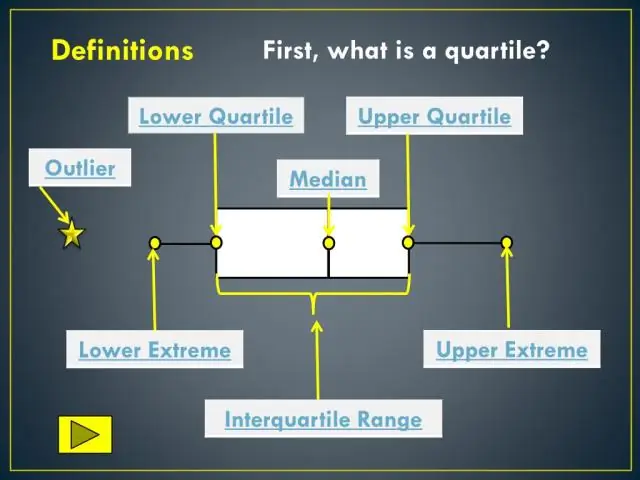

Vad är skillnaden mellan en box- och morrhårsplot och en boxplot?

En ruta och morrhårsplott (kallas ibland en boxplot) är en graf som presenterar information från en femsiffrig sammanfattning. I en ruta och morrhårsplott: boxens ändar är de övre och nedre kvartilerna, så boxen spänner över interkvartilområdet. medianen markeras med en vertikal linje inuti rutan

Vad är likheten och vad är skillnaden mellan reläer och PLC?

Reläer är elektromekaniska brytare som har spole och två typer av kontakter som är NO & NC. Men en programmerbar logisk styrenhet, PLC är en minidator som kan fatta beslut baserat på programmet och dess ingång och utdata